PCB layout 对防静电影响重大,所以必须在layout 前就得考虑ESD 防护问题,而不是在板子出来后才加以修正。加TVS二极管绝对是简单而实用的防ESD方式,但它还是需要在画线路图时就选好具体料号或封装,并在PCB 上留好位置,一旦在测试当中没办法通过时就可以把它加上再测,当然,如果不加TVS二极管也能通过那就更好了。如果没留位置且测试通不过,这是件麻烦事。TVS二极管应用时需要考虑layout,需要考虑泄放路径的最短化。再好的TVS二极管如果layout 不好,它同样没办法起到防ESD 的作用。不管选择怎样的TVS二极管,它们在电路板上的布局非常重要。TVS二极管布局前的导线长度应该减到最小,因为快速(0.7ns)ESD 放电电流在电感性布线上感应出很高的电压尖峰,影响ESD 保护的性能。另外,快速 ESD 脉冲可能在电路板上相邻(平行)导线间产生感应电压。如果上述情况发生,由于将不会得到保护,因为感应电压路径将成为另一条让浪涌到达IC 的路径。因此,被保护的输入线不应该被放置在其它单独、未受保护的走线旁边。

推荐的ESD 抑制器件PCB 布局方案应该是:应尽可能的滤除所有的I/O 口的干扰信号,靠近连接器/触点PCB 侧。

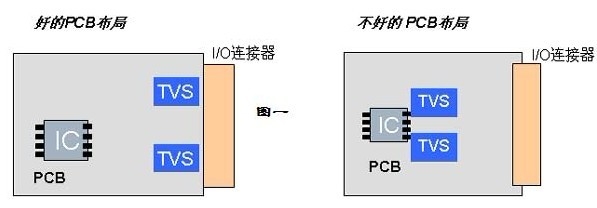

图一是PCB 布局的建议:走线时,尽可能缩短高频元器件之间的连线,设法减少它们的分布参数和相互间的电磁干扰;输入输出端用的导线应尽量避免相邻平行。最好加线间地线,以免发生反馈藕合。 |

|

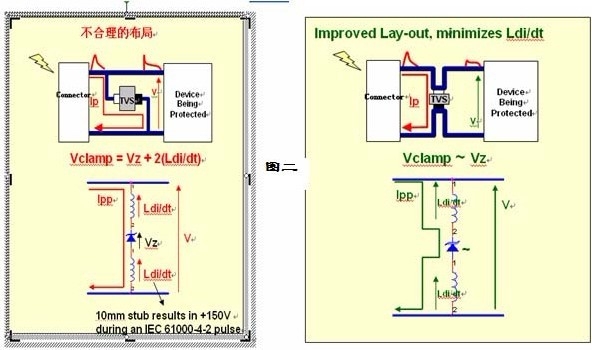

图二是布线时的优化建议:对于便携式设备来说,各类集成电路的复杂性和精密度的提高使它们对ESD 也更加敏感,以往的通用回路设计也不再适合。合理的PCB 布局最重要的是要在使用TVS 二极管保护ESD 损害的同时避免自感。ESD 设计很可能会在回路中引起寄生自感,会对回路有强大的电压冲击,导致超出IC 的承受极限而造成损坏。负载产生的自感电压与电源变化强度成正比,ESD 冲击的瞬变特征易于诱发高强自感。

|

|

减小寄生自感的基本原则是尽可能缩短分流回路,必须考虑到包括接地回路、TVS二极管和被保护线路之间的回路,以及由接口到TVS二极管的通路等所有因素。所以,TVS二极管应与接口尽量接近(直接就近泻放ESD 干扰,避免串入后续电路),与被保护线路尽量接近(画版时原则上要靠近被保护的芯片),这样才会减少自感耦合到其它邻近线路上的机会。

在电路板设计中还应注意以下几点:

1.避免在保护线路附近走比较关键的信号线;

2.尽量将接口安排在同一个边上;

3.避免被保护回路和未实施保护的回路并联;

4.各类信号线及其馈线所形成的回路所环绕面积要尽量小,必要时可考虑改变信号线或接地线的位置;

5.将接口信号线路和接地线路直接接到保护器件上,然后再进入回路的其它部分;

6.将复位、中断、控制信号远离输入/输出口,远离PCB 的边缘;

7.在可能的地方都加入接地点;

8.采用高集成度器件,二极管阵列不但可以大大节约线路板上的空间,而且减少了由于回路复杂可能诱发的寄生性线路自感的影响。

ESD 分析:

1.传导路径:在传导入口放ESD diode 就近泄放解决该ESD 干扰(最佳方案)。

2.失效分析:因为ESD 路径的难确定性,干脆就不去猜它到底是怎么传导的,而是直接去看那些被干扰到的IC。打静电后,IC 不会死而只是重起,那该是控制这些IC 的控制脚电位被改变了,是不是可以看这些IC 有EN 脚吗,电源有问题不?试着用示波器去看看静电从外壳传导到这些pin 脚后实际残留的波形,这更方便我们分析。然后在干扰的pin 脚处放ESD diode 保护该IC。 |

.jpg)